International Journal of Latest Trends in Engineering and Technology Vol.(8)Issue(2), pp.089-095 DOI: http://dx.doi.org/10.21172/1.82.014 e-ISSN:2278-621X

# DESIGN OF A LOW POWER AND HIGH SPEED MULTIPLIER

Shivani Siwach<sup>1</sup> and Suman Nehra<sup>2</sup>

Abstract- This paper is based on multiplier structure that has a lower power consumption as well as high speed compared with the conventional one. The reduction in power is achieved by applying Pass Transistor Logic (PTL) in Conventional Full Adder to improve the efficiency of the conventional multiplier structure. In this the full adder used in multiplier is replaced by a full adder using pass transistor Logic. The simulation of this multiplier is done using TANNER EDA. Finally, a low power and high speed proposed structure is implemented, which lowers the power consumption without considerably impacting the speed. The proposed structure is assessed by comparing their speed, power, and delay parameters with those of other existing multiplier using a 45-nm CMOS technology for a wide range of supply voltages.

Keywords - Multiplier, Pass Transistor logic

## I. INTRODUCTION

There is a rising requirement for low power VLSI which can be addressed at various design levels, such as the architecture, circuit, and the process technology. In the circuit level, the option for the saving of power do exists as a result of proper choice of a logic style for applying the combinational circuits.[1]This is due to all the factors which are controlling the power utilization, switching capacitance, and short-circuit currents are strongly determined by the preferred logic style. Depending on the application, the circuit to be implemented, and the technique used for design, several performance aspects become important, disallowing the configuration of universal rules for best logic styles[2].

A multiplier is one of the key blocks in most of the digital signal processing (DSP) systems. The diverse DSP applications where a multiplier plays a crucial role consist of digital filtering, digital communications and several more[3]. Computational performance of a DSP system is limited by its multiplication performance and since, multiplication dominates the execution time of most DSP algorithms, and therefore high-speed multiplier is much desired [4]. With an ever-increasing quest for greater computing power on battery operated mobile devices, design emphasis has shifted from optimizing usual delay time, area size to minimizing power dissipation while still maintaining the high performance. Hence designing of multipliers that offer any of the following design targets – high speed, low power consumption, less area or even a combination of them is of great interest[5].

### **II.CONVENTIONAL ARRAY MULTIPLIER**

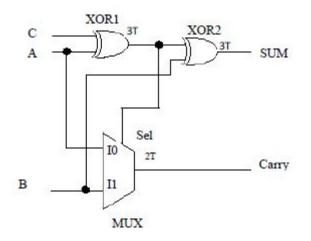

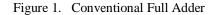

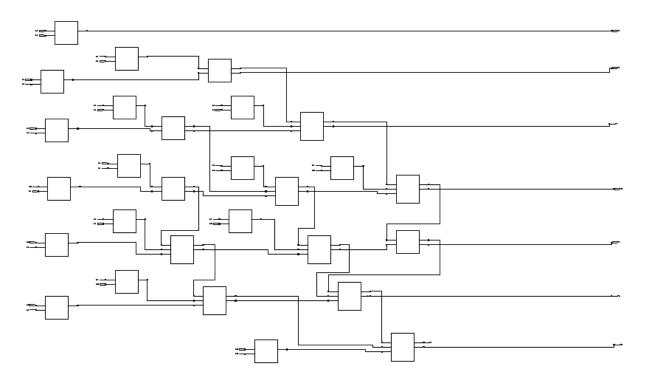

The conventional 4x4 array multiplier consists of 8-transitor(8-T) Full Adder, 5-transistor(5-T) Half Adder and 2-transistor(2-T) And gate.[6] The basic circuit layout of conventional Full adder (4 bit) is shown in Fig.1 and the schematic diagram of the multiplier is shown in Fig.2

<sup>&</sup>lt;sup>1</sup> Department of Electronics and Communication Engineering, Mody University of Science and Technology, Lakshmangarh, Rajasthan, India

<sup>&</sup>lt;sup>2</sup> Department of Electronics and Communication Engineering, Mody University of Science and Technology, Lakshmangarh, Rajasthan, India

#### III. PROPOSED ARRAY MULTIPLIER USING PASS TRANSISTOR LOGIC BASED FULL ADDER

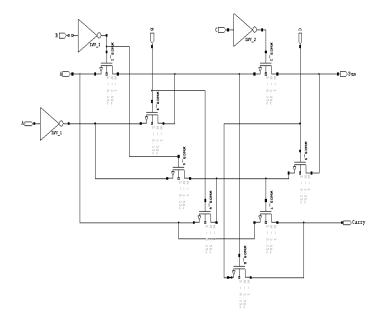

In Proposed Array Multiplier, the Full Adder is based on Pass transistor Logic for better operational characteristics of high speed and low delay (shown in Fig.3) and the schematic diagram of the Pass Transistor Logic based full adder used in proposed multiplier is shown in Fig.4.[7]Subsequently, the number of transistors are reduced in the Full Adder of the proposed multiplier . Since the number of transistors is reduced in the multiplier, it results in reduced area as well as delay.

Figure 3. Proposed Multiplier using Pass transistor logic based Full Adder

Figure 4. Pass transistor Logic Based Full Adder

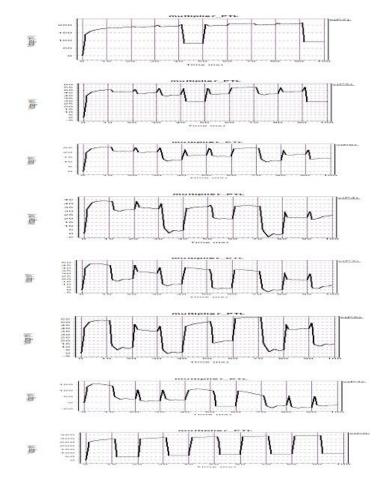

## IV.SIMULATION AND COMPARISON OF EXISTING MULTIPLIER AND PROPOSED MULTIPLIER

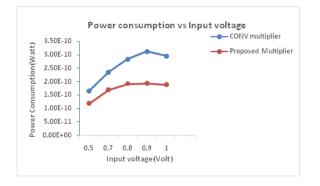

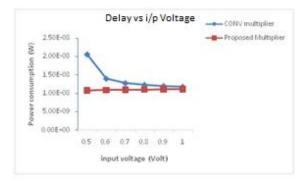

1. The graphs shown in Fig.6 and 7 depicts that the proposed Multiplier has better performance in comparison to the existing design [8].

Figure 6. Power consumption with varying input Voltage

Figure.7 Delay with varying input Voltage

It was found that proposed multiplier has 30-45% and 13-35% improvement in terms of power consumption and Delay with varying input voltage as compared to the existing multiplier respectively.

| Power Consumption vs Temperature |                                                                                           |     |            |              |             |         |                                            |

|----------------------------------|-------------------------------------------------------------------------------------------|-----|------------|--------------|-------------|---------|--------------------------------------------|

| ower Consumption (W)             | Power<br>3.50E-10<br>3.00E-10<br>2.50E-10<br>1.50E-10<br>1.00E-10<br>5.00E-11<br>0.00E+00 | Con | sump       | tion         | rs Tem      | iperatu | re<br>———————————————————————————————————— |

|                                  |                                                                                           | 10  | 20<br>Temp | 30<br>eratur | 40<br>e(°C) | 50      |                                            |

|                                  |                                                                                           |     |            |              |             |         |                                            |

Figure 8. Power Consumption varying temperature

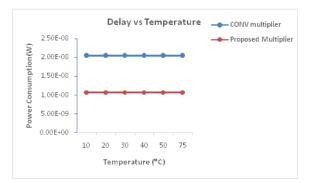

Fig.ure 9. Delay varying temperature

2. Fig.8 and 9 shows the proposed design has 63-70% and 23-45% improvement in power consumption and delay with varying temperature in comparison to the existing design Thus, the proposed design is efficient in power consumption at various system temperature as seen above.

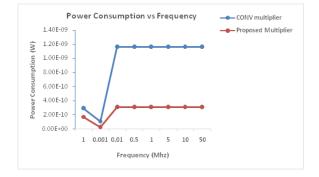

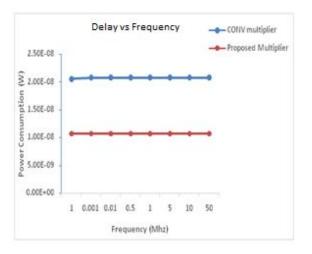

Figure 10. Power Consumption Varying Frequency

Figure 11. Delay Varying Frequency

3. Comparison in terms of power consumption and delay with varying frequency is shown in fig. 10 and 11 which illustrates that the proposed design has a lesser power consumption and delay as compared to the conventional one[9].

#### **V.CONCLUSION**

The synthesis result confirms that the proposed multiplier is suitable for low power and small area applications[10]. The Speed enhancement and lower power consumption was achieved by replacing the conventional full adder with the Pass Transistor Logic based Full Adder. The proposed circuit has been tested to have better temperature sustainability and significantly less power consumption. Again, the suggested structure showed the lowest delay and making itself as a better candidate for high-speed low-power applications.

#### REFERENCES

- Biswarup Mukherjee, Biplab Roy, Arindam Biswas, Aniruddha Ghosal," Design of a Low Power 4x4 Multiplier Based on Five Transistor (5-T) Half Adder, Eight Transistor (8-T) Full Adder & Two Transistor (2-T) AND Gate ", Proceedings of the IEEE, 2015.

- [2] lackuline Moni D, Anu Priyadharsini K," DESIGN Of LOW-POWER AND HIGH PERFORMANCE RADIX-4 MULTIPLIER ", Proceedings of the IEEE, International Conference on Devices, Circuits and Systems (ICDCS), pp.432-435,15-16 March 2012

- [3] S. Sabeetha, J. Ajayan, S. Shriram, K. Vivek, V. Rajesh," A Study of Performance Comparison of Digital Multipliers Using 22nm Strained Silicon Technology", Proceedings of the IEEE, IEEE sponsored 2<sup>nd</sup> International Conference on Electronics and Communication Systems, ICECS, pp. 180-184, 2015

- [4] Gaurav Verma, Sushant Shekhar, Oorja M Srivastava, Shikhar Maheshwari, Sukhbani Kaur Virdi," Low Power & High Performance Implementation of Multiplier Architectures ", Proceedings of the IEEE, International Conference on Computing for Sustainable Global Development (INDIACom), pp. 1989-1992, 2016

- [5] Priyanka Srivastava, Vishant, Rakesh K. Singh and R. K. Nagaria," Design and Implementation of High Performance Array Multipliers for Digital Circuits", Proceedings of the IEEE, 2013

- [6] Prof. S.Murugeswari, Dr. S.Kaja Mohideen," Design of Area Efficient and Low Power Multipliers using Multiplexer based Full Adder ", Proceedings of the IEEE, 2nd International Conference on Current Trends in Engineering and Technology, ICCTET, pp. 388-392,2014

- [7] K. Benarji Srinivas, Mohammed Aneesh Y.," Low power and high speed Row and Column Bypass Multiplier ", Proceedings of the IEEE, 2014

- [8] Ajeya Vallamdas, Arunkumar P Chavan, Dr SJagannathan," Design Of Low Power And Energy Efficient 5 X 5 Multipliers", Proceedings of the IEEE, IEEE International Conference on Recent Advances and Innovations in Engineering (ICRAIE-2014), May 09-11, 2014

- [9] N.Ravil, Y.Subbaiah, Dr.T.Jayachandra Prasad, Dr.T.Subba Rao," A Novel Low Power, Low Area Array Multiplier Design for DSP Applications", Proceedings of the IEEE, Proceedings of 2011 International Conference on Signal Processing, Communication, Computing and Networking Technologies ICSCCN ,2011

- [10] S.Srikanth, I.ThahiraBanu, G.VishnuPriya, G.Usha," Low Power Array Multiplier Using Modified Full Adder", Proceedings of the IEEE, 2nd IEEE International Conference on Engineering and Technology (ICETECH), 17th & 18th March 2016.